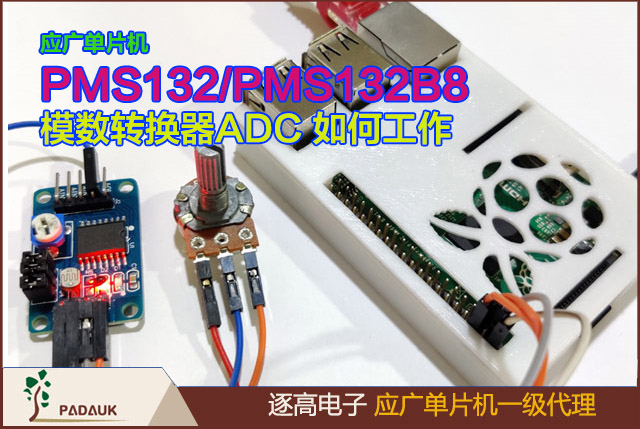

应广单片机 PMS132/PMS132B 8 位 OTP 型单片机带 12 位 ADC

特性

通用系列

不建议使用于 AC 阻容降压供电或有高 EFT 要求的应用。应广不对使用于此类应用而不达安规要求负责

工作温度范围:-40°C ~ 85°C

系统特性

2KW OTP 程序存储器

128 字节数据存储器

一个硬件 16 位计数器

两个 8 位硬件 PWM 生成器

三个 11 位硬件 PWM 生成器(PWMG0, PWMG1 & PWMG2)

提供一个硬件比较器

提供 1T 8x8 硬件乘法器

14 个 IO 引脚并带有上拉电阻选项

每个 IO 引脚都可设定唤醒功能

Bandgap 电路提供 1.2V 参考电压

高达 12 通道 12 位 ADC,其中一个通道来自于内部 bandgap 参考电压或 0.25*VDD

提供 ADC 参考高电压:外部输入,内部 VDD,Bandgap(1.20V),4V,3V,2V

时钟源:内部高频 RC 振荡器,内部低频 RC 振荡器和外部晶体震荡

对所有带有唤醒功能的 IO,都支持两种可选择的唤醒速度:正常唤醒和快速唤醒

8 段 LVR 复位设定:4.0V,3.5V,3.0V,2.75V,2.5V,2.2V,2.0V,1.8V

4 个可选的外部中断引脚

CPU 特点

单一处理单元工作模式

提供 87 个有效指令

大部分都是 1T(单周期)指令

可程序设定的堆栈指针和堆栈深度

数据存取支持直接和间接寻址模式,用数据存储器即可当作间接寻址模式的数据指针(index pointer)

IO 地址以及存储地址空间互相独立

引脚功能说明

模拟-数字转换器(ADC) 模块

当使用 ADC 模块时有 7 个寄存器需要配置,它们是:

ADC 控制寄存器(adcc)

ADC 调节控制寄存器(adcrgc)

ADC 模式寄存器(adcm)

ADC 数据高位/低位寄存器(adcrh, adcrl)

端口 A/B 数字输入启用寄存器(padier, pbdier)

如下是 ADC 装进程的步骤:

(1) 通过寄存器 adcrgc 配置参考高电压

(2) 通过 adcm 寄存器配置 AD 转换时钟信号

(3) 通过 padier

、pbdier 寄存器配置模拟输入引脚

(4) 通过 adcc 寄存器选择 ADC 输入通道

(5) 通过 adcc 寄存器启用 ADC 模块

(6) 启用 ADC 模块之后,延迟一段时间

条件 1:使用 bandgap 1.2V 或 2V/3V/4V 相关电路时,无论是将其用作内部参考高电压还是作为 AD 输入通

道,所需的延迟时间必须超过 1ms;如果 200 个 AD 时钟已经超过 1ms,那么延迟时间只需要 200 个 AD 时

钟即可。当启用内部 BG/2v/3v/4v 为参考高电压时,必须保证 IHRC 为开启状态。

条件 2:没有使用任何 bandgap 1.2V 或 2V/3V/4V 相关电路,延迟时间仅需 200 个 AD 时钟。

另注意:以上两条件所涉及的 200 个 AD 时钟,该时钟是指由 ADCM 寄存器配置后的 ADC 转换时钟而非系

统时钟 SYSCLK。

(7) 执行 AD 转换并检查 ADC 转换数据是否已经完成 adcc.6 设置 1 开启 AD 转换并且检测 adcc.6 是否是‘1’。

(8) 从 ADC 寄存器读取转换结果:

先读取 adcrh 寄存器的值然后再读取 adcrl 寄存器的值。

应用时,如果是关掉 ADC 模块后再重新启用 ADC 的情况下,或者在切换 ADC 参考电压及输入通道时,进

行 ADC 转换之前请重新执行如上步骤 6,确保 ADC 模块已经准备好。

AD 转换的输入要求

为了满足 AD 转换的精度要求,电容的保持电荷(CHOLD)必须完全充电到参考高电压的水平和放电到参考

低电压的水平。模拟输入电路模型如图 21 所示,信号驱动源阻抗(Rs)和内部采样开关阻抗(Rss)会直接影响到

电容 CHOLD 充电所需求的时间。内部采样开关的阻抗可能会因 ADC 充电电压而产生变化;信号驱动源阻抗会

影响模拟输入信号的精度。使用者必须确保在采样前,被测信号的稳定,因此, 信号驱动源阻抗的最大值与被

测信号的频率高度相关。建议,在输入频率为 500khz 下,模拟信号源的最大阻抗值不要超过 10KΩ。

PMC-APN001

ADC 模拟信号源输出阻抗应用需知

适用范围:所有带 ADC 单片机

外部电路输出模拟信号给 ADC 测量时,必须注意阻抗匹配的问题,否则 ADC 可能无法达到预期精确度。

外部电路输出阻抗必须与芯片的 ADC 脚位元输入阻抗匹配,才不会产生测量误差。待测信号必须在被取

样(sample)之前,达到该有的精度。就待测信号是在 0V ~ 5V 变化的极端条件来说,以外部信号源对

Chip 内部充放电的等效电路,如下图所示。

可以用下列公式表示其输入信号的精确度:

若以 10 bit 精确度而言,∆需小于 0.001(1/2 10);即待信号在被取样前,必须达到该有的 0.999 以上精确

度

以取样周期为 2us 而言,信号源的最高周期也是 2us,信号源对于芯片内部充放电,必须在被取样前有足

够的精确度。

芯片内部电容约 10pF,由于 ADC 对取样点充放电时间只有半个周期,所以 T 取为 1us。

若在开发使用上有任何疑问,请就近洽询我们的代理商,或与逐高电子开发部联系